## DISSERTATION

## INSTRUCTION SCHEDULING USING GENETIC ALGORITHMS

Submitted by

Steven John Beaty Department of Mechanical Engineering

In partial fulfillment of the requirements for the degree of Doctor of Philosophy Colorado State University Fort Collins, Colorado Fall 1991

## COLORADO STATE UNIVERSITY

October 29, 1991

WE HEREBY RECOMMEND THAT THE DISSERTATION PREPARED UNDER OUR SUPERVISION BY STEVEN J. BEATY ENTITLED INSTRUC-TION SCHEDULING USING GENETIC ALGORITHMS BE ACCEPTED AS FULFILLING IN PART REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY.

Committee on Graduate Work

$\operatorname{Adviser}$

Department Head

## ABSTRACT OF DISSERTATION

### INSTRUCTION SCHEDULING USING GENETIC ALGORITHMS

Genetic algorithms are a robust adaptive optimization technique based on a biological paradigm. They perform efficient search on poorly-defined spaces by maintaining an ordered pool of strings representing regions in the search space. New strings are produced from existing strings using the genetic-based operators of recombination and mutation. Combining these operators with natural selection results in the efficient use of hyperplane information found in the problem to guide the search. The searches are not greatly influenced by local optima or non-continuous functions. Genetic algorithms have been successfully used in problems such as the traveling salesperson and scheduling job shops. Instruction scheduling are also modeled as these types of problems, which motivated the application of genetic algorithms to this domain.

> Steven J. Beaty Department of Mechanical Engineering Colorado State University Fort Collins, Colorado 80523 Fall 1991

### ACKNOWLEDGEMENTS

As with all efforts of this magnitude, rarely does one work without a large amount of support.

My deepest thanks go to Phil Sweany, my compiler compadre, for his work on the ROCKET milieu, for his deep understanding of the problems involved in the translation of one language to another, and for his friendship that made all of this bearable.

I would like to thank my committee for their flexibility and interest in this work. Thanks go to Dr. Darrell Whitley for his expertise with genetic algorithms. My special thanks to Dr. Gearold Johnson, for recognizing Engineering when he sees it and for taking special care of me.

I would like to thank two members of the Usenet community: Thanasis Tsantilas (thanasis@cs.columbia.edu) for pointing me in the direction of Peter Winkler (pw@bellcore.com.) Peter provided me with an early copy of the work on counting linear extensions.

My family played a part, each contributing, both historically and recently, a part of themselves that has always helped me reach my goals.

A large part of my support for this effort came from my wife, Paula. She was there when I needed intellect, compassion, and someone to support me. She understood what I was going through, as she herself has walked the same path. If mine is the brain behind this work, hers is the soul.

This work was self-funded.

# DEDICATION

Dedicated to everyone who has bet on a dark horse that came in. In memory of Susan Gayle Kennedy.

# CONTENTS

| 1 Introduction                                                | 1  |

|---------------------------------------------------------------|----|

| 1.1 Microcode                                                 |    |

| 1.2 Compaction                                                |    |

| 1.2.1 Previous Methods                                        | 7  |

| 1.2.2 Heuristics                                              | 9  |

| 1.3 From Compaction to Instruction Scheduling                 | 11 |

| 1.4 Challenges                                                | 12 |

| 1.5 Requirements                                              | 13 |

| 2 The Scheduling Problem                                      | 16 |

| 2.1 A Formal Definition of the Instruction Scheduling Problem | 16 |

| 2.1.1 Adding Encoding Conflicts                               |    |

| 2.1.2 Types of Failures                                       |    |

| 2.1.3 Similar Problems                                        |    |

| 2.2 Representation                                            |    |

| 2.2.1 Dags and Orders                                         |    |

| 2.2.2 Enumerating Orders                                      |    |

| 2.3 Dags to Represent Data Dependence                         |    |

| 2.3.1 Necessary Edges                                         | 24 |

| 2.4 Timing on Edges                                           |    |

| 2.5 Timing on Nodes                                           |    |

| 2.5.1 Absolute Timing                                         |    |

| 2.6 Summary                                                   |    |

| 3 Compiler Technology                                         | 36 |

| 3.1 MILC Complexities                                         | 36 |

| 3.2 The ROCKET Compiler                                       |    |

| 3.2.1 Code Generation Phases                                  |    |

| 3.2.2 Machine Description                                     |    |

| 3.3 Reduction of Anti-dependencies                            |    |

| 3.4 Register Assignment                                       |    |

| 3.4.1 Terminology                                             |    |

| 3.4.2 Graph Coloring Register Assignment                      | 47 |

| 3.4.3 Interference                                            | 51 |

| 3.4.4 When?                                                   | 52 |

| 3.4.5 Results                                                 | 57 |

| 3.5 Summary                                                   | 59 |

| vi                                                            |    |

| 4 List Scheduling                                                                                                                                    | 60  |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.1 Methods                                                                                                                                          | 60  |

| 4.1.1 Specifics                                                                                                                                      | 60  |

| 4.2 Direction $\ldots \ldots \ldots$ | 65  |

| 4.3 Complexity                                                                                                                                       | 66  |

| 4.4 Heuristics                                                                                                                                       | 69  |

| 4.4.1 Specifics                                                                                                                                      | 70  |

| 4.4.2 Enumeration $\ldots$                                          | 73  |

| 4.4.3 Update Interval                                                                                                                                | 76  |

| 4.5 Foresight                                                                                                                                        | 77  |

| 4.5.1 Hindsight                                                                                                                                      | 79  |

| 4.5.2 Incremental                                                                                                                                    | 81  |

| 4.6 Lookahead                                                                                                                                        | 83  |

| 4.7 Summary                                                                                                                                          | 85  |

| 5 Genetic Algorithms and Instruction Scheduling                                                                                                      | 86  |

| 5.1 Foundations                                                                                                                                      | 86  |

| 5.1.1 GENITOR                                                                                                                                        | 89  |

| 5.2 Results from Related Work                                                                                                                        | 90  |

| 5.2.1 The Traveling Salesperson Problem                                                                                                              | 90  |

| 5.2.2 Job-Shop Scheduling                                                                                                                            | 91  |

| 5.2.3 A Warehouse/Shipping Scheduler                                                                                                                 |     |

| 5.3 Instruction Scheduling using Genetic Algorithms                                                                                                  | 94  |

| 5.3.1 Methods                                                                                                                                        | 94  |

| 5.3.2 Approaches                                                                                                                                     | 99  |

| 5.3.3 Studies                                                                                                                                        |     |

| 5.4 Summary                                                                                                                                          |     |

|                                                                                                                                                      |     |

|                                                                                                                                                      | 10  |

| 6.1 Conclusions                                                                                                                                      |     |

| 6.2 Contributions                                                                                                                                    |     |

| 6.2.1 DDD constraints                                                                                                                                | 114 |

| 6.2.2 List scheduling                                                                                                                                | 114 |

| 6.2.3 Genetic Algorithms                                                                                                                             | 115 |

| 6.3 Directions                                                                                                                                       | 116 |

| 6.4 Summary                                                                                                                                          | 117 |

| 7 REFERENCES 1                                                                                                                                       | 118 |

# LIST OF FIGURES

| 1.1  | A hypothetical machine word                          | 6  |

|------|------------------------------------------------------|----|

| 2.1  | Topological sort                                     | 21 |

| 2.2  | Original absolute timing algorithm                   | 28 |

| 2.3  | A graph where the absolute timing algorithm can fail | 29 |

| 2.4  | Update successor timing                              | 31 |

| 2.5  | Update predecessor timing                            | 32 |

| 2.6  | Update timing                                        | 34 |

| 2.7  | Example for the need to iterate                      | 34 |

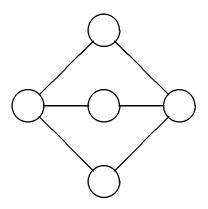

| 3.1  | A Pathological Graph                                 | 50 |

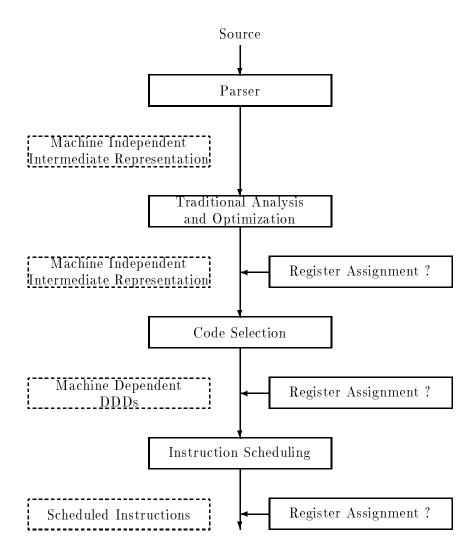

| 3.2  | Possible placements of register assignment           | 54 |

| 4.1  | List scheduling                                      | 61 |

| 4.2  | Exhaustive list scheduling algorithm                 | 62 |

| 4.3  | Non-exhaustive list scheduling                       | 64 |

| 4.4  | Critical path comparison                             | 70 |

| 4.5  | A DDD where the critical path heuristic fails        | 72 |

| 4.6  | A DDD where the heuristics compete.                  | 73 |

| 4.7  | Critical path competition                            | 77 |

| 4.8  | Need for dynamic schedule range calculation          | 78 |

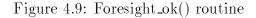

| 4.9  | Foresight_ok() routine                               | 79 |

| 4.10 | Schedule an operation using foresight                | 80 |

| 4.11 | Recursive foresight                                  | 82 |

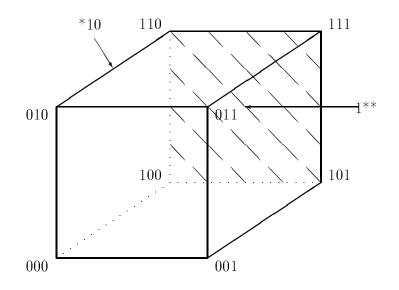

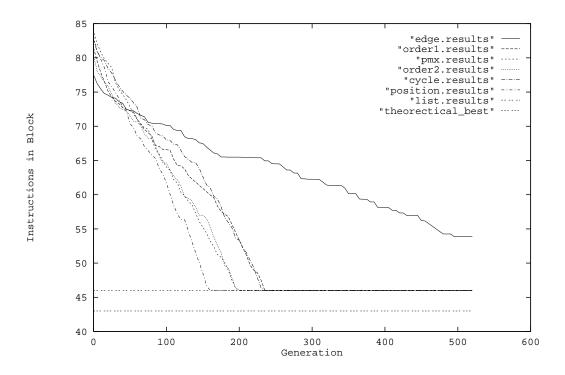

| 5.1 | Sampling in a three-dimensional hypercube |

|-----|-------------------------------------------|

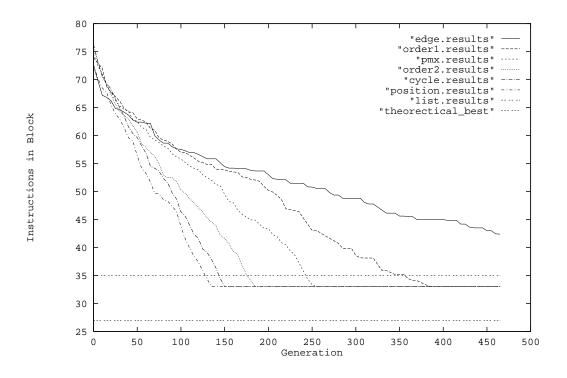

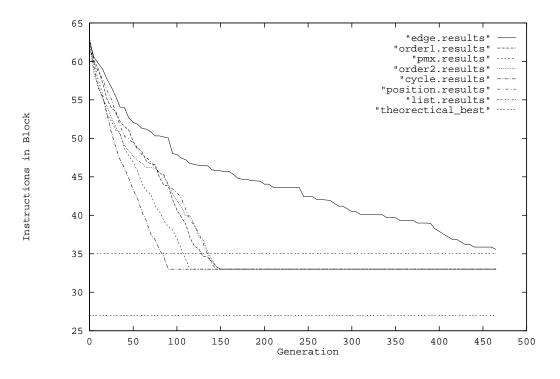

| 5.2 | Livermore Kernel Number 1                 |

| 5.3 | Livermore Kernel Number 2                 |

| 5.4 | Livermore Kernel Number 4                 |

| 5.5 | Livermore Kernel Number 8                 |

| 5.6 | Livermore Kernel Number 10                |

| 5.7 | Linpack cgefa.c                           |

## Chapter 1

#### INTRODUCTION

As the desire for computation speed is increasing at an apparently unbounded rate, different methods have been applied to increase the amount of computation accomplished in a given amount of time. One current approach is advanced by the Reduced Instruction Set Computer method [Kat85, PS81]. The basic tenet is to speed up the processor clock as much as possible. For this to occur, the processor must be simplified so deleterious physical effects, such as gate delay and the speed of light in the media, are reduced. With this simplification, each instruction cannot manipulate much information. The overall speed of the processor is increased by raising the basic clock rate to ever greater heights. These processors appear to work well in the general consumer computer field.

Another approach to increase the amount of computing work done per unit time is to increase the amount of information processed during each processor clock tick. Proponents of this approach purport that the inherent fine-grained parallelism found in virtually all computer programs will map better, and therefore run more rapidly on machines supporting some form of low-level parallelism. Fine-grained parallelism describes architectures implementing parallelism at an instruction or smaller level, thereby executing more than one operation in a single instruction cycle. Historically, machines exploiting this type of architecture have been application specific, realizing the inherent performance benefit while not being required to support general purpose computing. This type of system includes high-end graphics processors, language specific computers, and embedded systems. More general purpose processors are now becoming available that take advantage of this type of parallelism [KA91]. These machines may be contrasted to those with course-grained parallelism that rely on the parallelism present at the function/subroutine level for speed enhancement.

Of course these two opposing methods should not be taken to represent the entire spectrum of compute engine possibilities. The RISC approach has been termed "vertical" because of the way the code appears, with many short instructions. CISC has been termed "horizontal," with fewer long instructions. Most machines are somewhere on the "diagonal" continuum between the two. It might be clearer to picture a pyramid with RISC at the "top" and fine-grained parallel machines at the "bottom."

Terminology used to describe architectures continually evolves, making any description somewhat transient. This work will use the term "MILC" (Machine with Instruction-Level Concurrency), because no other term exists that describes all the types of machines instruction scheduling pertains to. At a minimum, a MILC has the ability to initiate more than one operation per instruction cycle, and therefore benefits from instruction scheduling. MILCs include at least the following as subsets:

- Complex Instruction Set Computers (CISCs). This type of machine has "highlevel" instructions that programming languages are (supposedly) easy to translate to. The VAX 11/780 [Pat89, Dig81] is an instance of a CISC; e.g. it includes an instruction operating on arbitrary polynomials.

- 2. Superscalar computers. These machines use hardware to determine whether operations can be executed simultaneously. The order instructions are presented to the execution unit can have a profound effect on the speedups possible, necessitating intelligent instruction ordering. Recent examples of this type of machine include the Intergraph Clipper [Pat90], the IBM RS6000 [IBM90], the MIPS chips [Kan87], and the Intel i860 [Int90].

- 3. Microcoded machines. Used as a basis for the instruction scheduling methods in this paper, they are discussed in Section 1.1.

- 4. (Very) Long Instruction Word ((V)LIW) architectures. These have replicated processing units with lengthy (currently up to 1000 bits) instructions containing the data and control information for each unit. Fisher [FERN84], Ellis [Ell86] and Colwell et al. [CNO<sup>+</sup>88] discuss VLIW architecture and translation methods suited for them. The Multiflow TRACE series of computers were based on VLIW techniques. VLIW architectures have both local and shared processor memories, an issue not addressed here.

### 1.1 Microcode

This work leverages previous work done in microarchitectures. Much of today's MILC heritage lies in yesterday's microcoded machines. The visibility of underlying machine features is the most pronounced similarity. To forestall any confusion regarding the use of the term "microcode," some clarification is necessary. The microcode world has been divided into four distinct groups. Tredennick [Tre82] enumerates these various "cultures" of microprogramming:

- The commercial machine culture uses microprogramming to implement a single instruction set on a variety of differing machines. The IBM System/360 [AST67] are good examples of machines with various internal hardware microprogrammed to accept the same "high-level" assembler language.

- The bit-slice culture uses generic bit-slice components programmed to perform one specific task. These machines are generally programmed by their designers so high performance is achieved. However, there currently is interest in having the end user program these machines to better match the machine and its intended application. The AMD2900 is an example of this type of architecture [Adv85].

- The microprogrammable machine culture builds machines intended to execute native code for various architectures by modifying (at run time) the microcode control store. The Nanodata QM1 is an example of this type of machine [KD81, Nan74].

- The single chip culture has a control store (usually a Read Only Memory) on the chip which is microprogrammed. A processor of this type is microcoded as an implementation technique and the microcode usually manages the low-level register-to-register and register-to-functional-unit transfers. The Motorola 68000 series chips are an example of this type of "microprogramming" [HL85].

This work is targeted to, and MILCs are related to, the bit-slice culture. The other three cultures are based on implementing a specific instruction set in the target machine. Implementing instruction generally requires short sequences of microcode independent from one another. Compilers are less useful for this type of code because both the amount of program information and the amount of global optimization possible are less.

Traditionally, fine-grain architectures have been programmed by hand, and in some sense "close" to the actual hardware. There have been few programming abstractions used in order to fully utilize the available resources. Compilers become useful when complex control and data structures are desired to increase programmer productivity. Compilers also allow persons not intimately familiar with an architecture to use it effectively. If a compiler can use the resources present in a machine, e.g., as effectively as hand-generated code, there is no reason to hand code. It has been shown that, for the most part, programmer output is invariant upon the language chosen. This speaks to the usefulness of high-level languages when creating, modifying and maintaining any code.

The use of microcode has advantages beyond the basic one of speed. In [Veg82] four more advantages are listed:

- *Flexibility*. Many design decisions can be delayed until later in the design cycle.

- *Extensibility.* Once an architecture is on the market, it can be extended with additional microcode, perhaps to tailor the machine to a specific application.

- *Cost.* The number and type of components can be reduced using a microcoded control store; the information density is higher in such a store compared to hardwired logic.

- *Simplicity.* Complex instructions such as string compare and table translation, both of which are simple algorithmically, are simple to realize in microcode.

### 1.2 Compaction

Because this work owes much to previous work done in microcode compaction techniques, a review is in order. A thorough survey of local compaction techniques is found in [LDSM80]; much of this section's terminology and content relies on that paper. Microprogrammable processors allow the simultaneous control of multiple hardware resources. This is achieved by not greatly encoding the control word of the machines. Compaction involves choosing, from the large solution set of possible concurrent instructions, one packing that hopefully reduces both the execution time and the space of the program.

A microprogram is composed of *microinstructions (MIs)*. During execution, the MI is the control word for the machine. Each separate machine operation within an MI is called a *microoperation (MO)*. A *field* within the instruction word of a machine controls a primitive machine activity. An MO may use one or more fields in order to execute its functionality. Expanding upon the earlier definition, if only one or a very few MO's fit within a machine's MI, the machine is said to be *vertical*. Conversely, if many MOs fit in an MI, the machine is said to be *horizontal*. See figure 1.1 for a fictional MI with 64 bits. This particular MI has fields to control the behavior of

|              | adder 1 | adder 2 | $\mathrm{mult}/\mathrm{div}$ | shifter | addr. gen. | cond. code | $\operatorname{const}$ |  |

|--------------|---------|---------|------------------------------|---------|------------|------------|------------------------|--|

| 6            | 4 5     | 4 4     | 4 29                         | 9 2     | 1 9        | ) 5        | 5 1                    |  |

| Bit Position |         |         |                              |         |            |            |                        |  |

Figure 1.1: A hypothetical machine word

two adders, a pipelined multiply/divide unit, a barrel shifter, an address generator, a condition code register, and has room for program constants. Each operation is independent of all others, allowing a large amount of instruction-level parallelism.

A straight line microcode sequence (SLM) is a set of MOs with a single entry at the top and a single exit at the bottom. These are also known as basic blocks. When a function is performed on one SLM, the function is termed local. If a function is performed on multiple SLMs, the function is called global. Data dependency analysis provides the partial ordering on the MOs, by representing in some form (usually a dependence graph) the semantic-preserving flow of data of the original program. Semantics are said to be preserved if, after a transformation, a program produces an identical set of outputs when given an identical set of inputs. Conflict analysis determines whether or not a set of MOs can fit within a given MI without violating the constraints of the processor. Compaction has been erroneously termed horizontal optimization; horizontal improvement is more to the point as it cannot guarantee optimality without exponential time.

The problem compaction tries to solve then, is placing a group of microoperations necessary for correct execution of the algorithm into as few microinstructions as possible. An optimal answer has been shown by DeWitt [DeW76] to be NPcomplete, i.e. computationally intractable. There are many problems related to compaction such as the Traveling Salesperson Problem and processor scheduling problem but, Landskov et al. [LDSM80] states compaction is an example of jobshop scheduling, giving a direction of attack.

#### 1.2.1 Previous Methods

Astopas and Plukas [AP71] are credited with developing the first method of microcode compaction. Their method examines all combinations of MOs that do not violate data dependencies, and chooses the combination, containing no resource conflicts, producing the shortest MI sequence. This is an exhaustive method and cannot be bounded by reasonable execution time. Landskov et al. [LDSM80] elucidate four methods of non-exhaustive microcode compaction that follow.

*Linear Analysis* (LA), developed by Dasgupta and Tartar [DT76], works on an SLM, starting with an empty list of MIs. It attempts to add MOs in the order they appear in the SLM into an existing MI. If LA cannot find an MI that can accept all the constraints on the MO, it creates a new MI and places the MO into it. The word "linear" describes the method of examining MOs in the SLM, not the execution complexity. To search for a place for an MO within a list of existing MIs, LA starts at the bottom of the list and proceeds upwards until a data dependency stops the process. This finds the earliest MI the MO under consideration may be placed. This location is termed the rise limit. Now the MIs are searched for resource conflicts that disallow packing of the MO. If a rise limit was found, this search proceeds back down the list of MIs. If no MI below the rise limit can accept the MO, a new MI is placed at the rise limit to allow other MOs data dependent upon the current one to be placed as high as possible. If no rise limit was found and no MI can accept the current MO, a new MI is placed above the top of the list and the current MO is placed into it. This, as before, reduces data dependence as much as possible. LA is a first come, first served algorithm that places MOs as high as possible in the MI list.

The *Critical Path* (CP) method, used by Ramamoorthy and Tsuchiya [RT74], determines how few MIs can be used for the given set of MOs, and first places the MOs that must occur at a certain time for the schedule to be optimal. The minimum length for a list of MIs is simply the depth (length of the longest path) of the dependence graph. First, an *early partition* of MOs is formed. This schedules MOs into "frames" based only upon their data dependence relationship. All nodes in the graph at the same level are "scheduled" to occur at the same time, disregarding any resource conflicts. After the early partition is formed, a *late partition* is produced in an analogous method. The late partition is a "bottom up" early partition. In fact, if the dependence graph is represented by an adjacency matrix, the late partition may be computed by inverting the matrix and applying the early partition algorithm. With these two sets generated, the *critical partition* calculation is simple: any MO having an identical early and late partition is in the critical partition. For an optimal schedule, an MO in the critical schedule must be placed within an MI on its level in the critical partition. Because resource and encoding conflicts have not yet been considered by CP, this is not always possible. A revised critical path is formed by taking these conditions into account and placing critical path MOs in MIs. The next step is to place all remaining non-critical MOs within the critical path MIs. Resource and data dependent conflicts also arise during this process, possibly necessitating the addition of more MIs to the list.

Branch and bound (BAB), promulgated by Yau et al. [YST74], creates a tree whose nodes represent microinstructions. A path from the root to a leaf corresponds to one possible ordering of microinstructions. The tree branches whenever there is more than one possible MI that could be placed at a point in the MI list. If the tree is complete, it represents all possible MI orderings and is known as BAB exhaustive. It runs in exponential time and space based on the size of the MO list. Heuristics are usually used to prune apparently extraneous branches from the tree. This can make the time polynomial but is not guaranteed to produce an optimal answer. If the algorithm finds a path the length of the longest path through the dependence graph, it has found an optimal answer as noted above and may stop the search. The branching may also stop if the shortest path through the tree so far is remembered and compared to all new paths. At every node, BAB attempts to form as complete an MI as possible. BAB examines the *data ready set (DRS)* for each MI it processes. The DRS is the set of MOs not data dependent upon any unplaced MOs. Multiple MIs can be formed from the DRS, by permuting its order, and because it is unknown which will produce a shorter schedule, branches are made for each.

List Scheduling (LS) is BAB with only one branch followed at each node. LS chooses the branch that appears to contribute the most in producing a short, valid schedule. List scheduling starts with an initially empty MI list, and MOs are placed within this list when they are:

- 1. data ready (that is, when all the resources they depend upon have the necessary values), and

- 2. highest on the data ready list as judged by a weighting heuristic.

This weighting function has great influence upon the final schedule and therefore must be chosen with care.

#### 1.2.2 Heuristics

All methods thus far rely on heuristics to remove the examination of parts of the search space that appear fruitless. Linear analysis tries to place MOs in the highest possible MI, reducing interference with other MOs needing placement. It also uses a first come, first served order on the MOs. Critical path places MOs not on the critical path heuristically. Branch and bound reduces the building and searching of the trees by guessing which branches will not lead to more compact code. The packing of MOs into MIs is ranked according to some metric. List scheduling has a similar approach in that MO placement is based on a set of weights assigned to each MO. The MO placed next in the MI list is the one on the data ready list with the highest weight.

Using heuristics can be difficult when attempting to arrive at an efficient yet efficacious compactor. This difficulty is compounded by several factors. The heuristics generally must be regenerated for each machine targeted. The heuristics themselves are not in a form easily understood by humans, thus making it difficult for humans to correctly guess and modify a compactor's behavior. It is also possible the heuristics do not address an issue having great import on the final code. Heuristics that work well for one ordering of MOs may not work well for another.

As noted before, the entire compaction problem is NP-complete. There are currently no methods guaranteed to produce optimal MI schedules without requiring either exponential time or space, or both. Because all previous methods rely on heuristics to reduce the amount of time used to obtain a solution, they are intimately bound to the heuristics chosen. These heuristics are picked before the execution of the compaction routine and remain static throughout. They have no ability to learn from previous runs or to take advantage of anomalous situations existing in specific compaction situations that lead to shorter code sequences. It would be desirable to use a search technique that does not involve heuristics yet provided a robust and efficient examination of the problem space. If such a method is available, and its execution time can be easily bounded, its application to the microcode compaction problem would be attractive.

Recent efforts have focused on inter-block compaction as well. Trace scheduling and percolation scheduling are two methods. Trace scheduling extends local compaction methods by allowing them to operate on more than one block at a time [Fis81, HMS87]. A trace is a loop-free section of code containing multiple basic blocks. When an entire trace is scheduled, the possibility for creating incorrect code, by moving operations past branches, arises. A bookkeeping phase makes copies of operations along other traces to correct the semantics. Traces are chosen in order of most-likely-to-execute first. Other traces can then be compacted. This emphasizes the frequently traversed paths at the possible expense of the infrequently traversed ones. This method relies upon the availability of good quality local compactors.

Percolation scheduling, as described by Nicolau [Nic85] and Aiken and Nicolau [AN88], has a small set of operations allowed between MIs in a program graph. These allow deletion of empty MIs, non-flow-control MO motion, movement of a conditional jump, and removal of redundant MOs. The operations are defined so program semantics are always preserved. Inverses of these functions are also allowed. The application of the operators is guided by higher-level heuristics.

Vegdahl [Veg82] states that more emphasis needs to be given to local compaction. Fisher et al. [FLS81] state that list scheduling may not be general enough for advanced compaction techniques. Wijaya and Allan [WA89] conclude "Local compaction methods other than list scheduling should be considered." This work will explore local compaction only, with the assumption that producing quality local schedules can improve intra-block methods.

## 1.3 From Compaction to Instruction Scheduling

General instruction scheduling is concerned with many of the same issues as microcode compaction. As noted before, there is increasing visibility of underlying hardware features so that intelligent exploitation of these features result in increased run-time performance. These features remain hidden from the casual programmer in order to speed the development of useful end-user code. Historically, when a particular routine needed enhanced performance, a human would hand code a *vertical migration* (to lower levels of machine abstraction) in order to increase speed. With the advent of language translation tools that take advantage of difficult-to-program architectural features, all programs generated benefit from a "virtual vertical migration."

While this work is based upon microcode compaction, different terms will be used in order that compaction will be easily differentiable from instruction scheduling. The term *operation* will replace microoperation, and *instruction* will likewise replace microinstruction. This minor change in naming is important as it communicates visibility. Terms prefaced with micro are invisible to the casual user of an architecture. These types of features must be addressed by someone intimate with the entire design of the machine.

#### 1.4 Challenges

With all the advantages, why aren't there more horizontal processors? A typical MILC may be characterized by wide-word instructions, heavily pipelined functional and execution units, Single Instruction/Multiple Data (SIMD) processing, and complex timing between operations. These all add to the complexity for generating efficient software for this type of processor. Because such architectures are designed for efficient exploitation of fine-grain (low-level) parallelism, hand programming at the machine level is a slow, tedious, and exacting process. The use of higher-level tools has met resistance because it was felt these tools would remove the advantages these architectures have by not properly exploiting the machine's resources. If all the resources are not kept busy, the machine will be executing in a RISC-like fashion, albeit at a slower clock rate. When a large investment has been made in the development of hardware, the software must wring out all possible performance.

These architectures have multiple, and often replicated, functional units. This allows for many arithmetic, logical and addressing functions to be performed per clock cycle. Each of the functional units can access different types of data contained in different types of memories such as immediate fields, CPU registers, and off-chip memories. A benefit realized by MILCs is the lack of the communication bottleneck found in MIMD computers, because resource usage can be determined before the program is run. Each instruction is broken into many fields, each field controlling a different aspect of the architecture. There is complexity inherent in filling each field in each instruction, and this may be complicated by the presence of pipelined functional units. These units compute complex results, such as floating point multiplication or division, requiring more than one cycle of the clock. Operands are placed in the pipe and the results are available after some specified number of clock cycles. Properly filling and emptying all pipes is crucial in taking the fullest advantage of the machine.

Another difficulty in programming these machines is the nature of the code to be run on them. The trend, escalated by rapidly dropping memory prices, is to place more and more code into lower levels of machine abstraction to receive the speed benefit associated with this migration. The lifetime of processors in general is also decreasing, requiring that code be generated more frequently. All of this speaks to a need for tools to automate part of the difficult process of MILC code generation. Tools would allow programmers removed from the design process to use the architectures in their fullest potential.

#### 1.5 Requirements

What should tools do to increase the usefulness of MILC machines? There are several principles that would increase their acceptance.

The first is machine abstraction. The use of a high level language would increase the number of potential end users by decreasing the learning curve required to program a machine. The rapid spread of the C/UNIX (tm) environment to many platforms displays the benefits of having a machine abstraction. If the end users are already familiar with the high level language chosen for the tool, the speed they can write useful programs is, of course, notably increased.

The second issue is retargetability. The lifecycle for all architectures is decreasing, necessitating the migration of code from one generation of a processor to another. Tools, such as high level languages that directly specify desired algorithms, ease this burden by providing the capability of rapid transference of working code from one machine to another. If the description of the machine is not static within the tools, only the machine description needs to change between differing architectures. The descriptions of the algorithms and the tools using the machine description remain unchanged between platforms. This would also remove the need for end user familiarity with the minutiae of the machine, and free the designers from the task of providing continuing support. The designer could provide a description for the tools and return to other projects.

The third issue is optimization. This involves reducing both the (usually opposing) time and space requirements for a program. For tools to be accepted by the programming community, they must produce quality code. There is no absolute measure for the quality of produced (correct) code, but the margin quoted by some is two to three times as long in time and space complexity as a human who is very proficient on a given architecture [BDM+88]. This is a tall order for automated tools to provide, but not an unreasonable one given the current state of the art. As has been mentioned before, the tools must utilize the available resources well so they do not turn a MILC into a slow, expensive, RISC. Also, because this programming is at the lowest level of a system, its efficiency directly influences the efficiency of the rest of the system.

The advantages to have automated code generation tools for horizontal machines are manifold. Code can be generated for a machine before it is committed to silicon. This can point out bottlenecks in the architecture design that would confound both humans and tools alike. This interaction could close the design loop between hardware and its associated software, benefiting the total performance of the system. Most hardware in the past has been designed in a vacuum; input from software engineers was usually neither encouraged nor accepted. With increasing performance competition from many areas, this sort of designing becomes more difficult to tolerate as it negatively influences the overall system performance.

There should also be more confidence that the system will achieve its goals. This is especially true of migrating code from one platform to another. If an algorithm description produces working code for one, there should be reason to believe that it will work for another. The transference of code to higher performance versions of an architecture should be particularly straightforward. Tools would provide the capability to "hit the ground running" with a new machine. The software could be written at the same time the hardware is being designed/debugged/produced.

To realize all these benefits, multiple tools are required. The first is a compiler to take some form of high level algorithm description and produce well optimized code as output. An assembler usually receives this code and produces machine executable code. This allows the flexibility of human created assembly code should some critical section require intervention. This intervention should not be necessary with a well written compiler/optimizer, and a better response to this impulse would be to redirect the effort required to hand tune the code into improving the compiler's ability to generate quality code. A retargetable simulator is needed for checking, before and after the machine is in silicon, the conformity and efficiency of the code produced by the compiler. All the tools should be based upon one coherent, complete machine description. This allows for rapid retargeting.

This work is only concerned with a compiler's generation of quality code and assumes a supportive environment is available.

### Chapter 2

## THE SCHEDULING PROBLEM

Much work has been undertaken in methods that schedule event occurrences. This has been, in part, motivated by the impact that quality scheduling imparts to many diversified areas. In Coffman [Cof76], a thorough treatment is given to many different kinds of scheduling problems. The general scheduling problem is there stated as

is there a schedule for the set of n tasks  $T_1, T_2, \ldots, T_n$  with precedence constraint  $\prec$  and execution times  $\tau_1, \tau_2, \ldots, \tau_n$ , on m processors with finishing time  $\omega$  or less?

This problem has been shown to be NP-complete. Coffman [Cof76] further states that even by restricting the scheduling problem various ways (i.e. an empty precedence constraint and only two processors) the problem is still NP-complete. DeWitt [DeW76] shows the Local Compaction Problem is NP-complete by simplifying it to the Unit Execution Time Scheduling Problem, another known NP-complete problem. With the assumption that  $P \neq NP$ , exhaustive search for an optimal answer is usually out of the question.

## 2.1 A Formal Definition of the Instruction Scheduling Problem

Gasperoni [Gas89] gives the formal definition of the *Local Compaction Problem* that follows. Let  $\mathbf{N}$  be the set of naturals and  $\mathbf{Z}$  be the set of integers. Given:

1. a machine  $\mathcal{M}$ , a set of resources  $\mathcal{R} = \{r_1, \ldots, r_m\}$  that the machine possesses,

- 2. a resource configuration vector  $\vec{\mathcal{R}}_{\mathcal{M}}$  of  $\mathbf{N}^m$ , where the *k*th entry of  $\vec{\mathcal{R}}_{\mathcal{M}}$  (denoted  $\vec{\mathcal{R}}_{\mathcal{M}}(k)$ ) gives the number of units of resource  $r_k$  available in the machine configuration <sup>1</sup>,

- 3. a set of l operations  $\mathcal{O} = \{op_1, \ldots, op_j, \ldots, op_l\},\$

- 4. a duration function  $d : \mathcal{O} \to \mathbf{N}$ , where  $d(op_j)$  if the number of machine cycles  $op_j$  takes to execute,

- 5. a resource usage function  $\vec{\mathcal{R}_{\mathcal{O}}}: \mathcal{O} \times \mathbf{Z} \to \mathbf{N}^m$  ( $\vec{0}$  is the null vector):

$$\vec{\mathcal{R}_{\mathcal{O}}}(op_j, X) = \begin{cases} \text{the vector of the } x \text{th step of } op_j & \text{if } 0 \le x < d(op_j) \\ \vec{0} & \text{otherwise} \end{cases}$$

the kth entry of  $\mathcal{R}_{\mathcal{O}}(op_j, X)$  (denoted  $\mathcal{R}_{\mathcal{O}}(op_j, X)(k)$ ) gives the number of units of resource  $r_k$  needed in the xth time step of operation  $op_j$ ,

- 6. a data dependence dag  $DDD = (\mathcal{O}, \mathcal{E})$  imposing a partial ordering on  $\mathcal{O}$  (DDD embodies the data dependences of  $\mathcal{O}$ 's operations),

- 7. a delay function  $\delta : E \to \mathbf{N}$ , defined on the edges of DDD, where for  $e = (op_{j_1}, op_{j_2}), \delta(e)$  is the delay that has to be respected before scheduling  $op_{j_2}$ , once  $op_{j_1}$  has been scheduled.

The goal of the Local Compaction Problem is to find a schedule  $\sigma : \mathcal{O} \to \mathbf{N}$ such that:

- 1. minimality:  $\sigma$  is of minimum length. The length of a schedule  $\sigma$ ,  $len(\sigma) = \max_{op \in \mathcal{O}}(\sigma(op) + d(op))$

- 2. dependence constraints:  $\forall e = (op_{j_1}, op_{j_2}) \in E, \sigma(op_{j_2}) \sigma(op_{j_1}) \ge \delta(e)$

<sup>&</sup>lt;sup>1</sup>ROCKET allows easy expression of a replicated storage and functional resources.

resource constraints: define vector addition the usual way, and vector comparison ≤ to be: v<sub>1</sub> ≤ v<sub>2</sub> ↔ ∀k{k | 0 ≤ k ≤ m} v<sub>1</sub>(k) ≤ v<sub>2</sub>(k), then the resource constraints are:

$$\forall t \{t \mid 0 \le t \le len(\sigma)\} \sum_{j=1}^{l} \vec{R_{\mathcal{O}}}(op_j, t - \sigma(op_j)) \prec \vec{R}_{\mathcal{M}}$$

### 2.1.1 Adding Encoding Conflicts

An issue the above definition does not address is that of *encoding conflicts*. These can occur within an instruction if more than one operation uses the same field. A way of adding this complication, similar in nature to resource conflicts, to the Local Compaction Problem follows. Given:

- 1. a field configuration vector  $\vec{\mathcal{F}}_{\mathcal{M}}$  of  $\mathbf{N}^m$ , where the *k*th entry of  $\vec{\mathcal{F}}_{\mathcal{M}}$  (denoted  $\vec{\mathcal{R}}_{\mathcal{M}}(k)$ ) gives the number of units of field  $f_k$  available in the machine configuration <sup>2</sup>,

- 2. a field usage function  $\vec{\mathcal{F}_{\mathcal{O}}}: \mathcal{O} \times \mathbf{Z} \to \mathbf{N}^m$  ( $\vec{0}$  is the null vector):

$$\vec{\mathcal{F}_{\mathcal{O}}}(op_j, X) = \{ \begin{array}{ll} \text{the field use of the } x \text{th step of } op_j & \text{if } 0 \leq x < d(op_j) \\ \vec{0} & \text{otherwise} \end{array}$$

the kth entry of  $\vec{\mathcal{F}_{\mathcal{O}}}(op_j, X)$  (denoted  $\vec{\mathcal{F}_{\mathcal{O}}}(op_j, X)(k)$ ) gives the number of units of field  $f_k$  needed in the xth time step of operation  $op_j$ ,

The schedule  $\sigma$  must be consistent with:

$$\forall t \{t \mid 0 \leq t \leq len(\sigma) \sum_{j=1}^{l} \vec{F_{\mathcal{O}}}(op_j, t - \sigma(op_j)) \prec \vec{F}_{\mathcal{M}}.$$

$<sup>^2\</sup>mathrm{ROCKET}$  allows easy expression of a replicated fields.

#### 2.1.2 Types of Failures

With this definition, three types of failures are possible [SDX87].

- *Timing failure:* at least two paths do not allow a correct partitioning due to incompatible timing.

- *Resource failure:* there does not exist enough of a certain resource to allow a correct partitioning in the target machine.

- Scheduling failure: the algorithm used does not find a correct partition when one is available in the DDD.

The first two failures are not produced in any architecture that supports all the semantics of the source. It is the last item addressed in this work.

### 2.1.3 Similar Problems

As mentioned before, the Local Compaction Problem is said, in Landskov et al. [LDSM80], to be similar to the Job-Shop Scheduling Problem. Coffman [Cof76] demonstrated that Job-Shop Scheduling is an NP-complete problem. Coffman also proposes several polynomial methods for attacking the problem, one of which is *list scheduling*. Chapter 4 goes into detail about the list scheduling algorithm. With the similarity to Job-Shop Scheduling, an investigation into methods producing good results for that problem should be explored for use in instruction scheduling.

## 2.2 Representation

The choice of how to represent a problem in a data structure often plays a major role in how the problem is solved. This allows the benefit of using existing algorithms along with the possible deleterious effects of using existing algorithms (i.e. using methods ill-suited for the current application.) A natural representation of dependencies between program operations has been that of a directed acyclic graph (dag). Operations are only dependent upon operations preceding them, resulting in the acyclic nature of the graph. Nodes in a dag represent the operations that must be executed in order to perform the semantics specified in the source. Usually additional information is included in each node to identify both the fields needed and the resources used and defined by the operation. This provides all the information needed by the scheduler at each node.

#### 2.2.1 Dags and Orders

Edges provide a *partial order* on the nodes such that an edge between nodes specifies when nodes can execute relative to each other. [Knu73] defines a partial order on a set S is a relation between the objects of S, denoted with " $\preceq$ ," satisfying the following properties for any objects x, y, and z (not necessarily distinct) in S:

- 1. If  $x \leq y$  and  $y \leq z$ , then  $x \leq z$ . (Transitivity.)

- 2. If  $x \leq y$  and  $y \leq x$ , then x = y. (Antisymmetry.)

- 3. If  $x \preceq x$ . (Reflexivity.)

If  $x \leq y$  and  $x \neq y$  then we write  $x \prec y$ .  $\leq$  is termed "precedes or is equal to", and  $\prec$  is termed "precedes." For the relation  $\prec$ , transitivity is defined as are the two additional properties:

- 1. If  $x \prec y$ , then  $y \not\prec x$ . (Asymmetry.)

- 2.  $x \not\prec x$  (Irreflexivity.)

Either way of defining partial order may be used where appropriate.

Given a partially ordered dag, a question that arises is determining the *total* orders consistent with the partial order. That is, to embed the partial order in a linear order, i.e., to arrange the objects into a linear sequence  $a_1, a_2, \ldots, a_n$  such that whenever  $a_j \prec a_k$  we have j < k [Knu73]. A method for producing this result

```

topo_sort (dag) {

set Q = dag(N) \{ \forall a, N \mid a \prec N = \emptyset \};

while (Q \neq \emptyset)

{

x = z \{ z \mid z \in Q \};

print x;

dag - x;

Q - x;

Q \cup y \{ \forall a, y \mid a \prec y = \emptyset \};

}

```

Figure 2.1: Topological sort

is called a *topological sort*. Figure 2.1 gives an algorithm for topologically sorting a dag from Hecht [Hec77].

A desirable property the topological sort algorithm has is the operation is *possible* for every partial ordering. This means it will always produce a total order, of the possibly many available, given a partial order. Topological sorting is one method of creating total orders from partial orders, but certainly not the only method.

#### 2.2.2 Enumerating Orders

The number of edges in a dag are a concern because they limit the number of different possible total orders. A lower and upper bound can be calculated to demonstrate this. In a completely inter-connected dag, the number of different possible orderings is

$$D(N,E) \prod_{l=0}^{l < =levels} (\text{number of nodes in } l)!$$

The *level* of a node in a dag is defined to be length of the longest path from the roots to the node. This formula can be derived by observing that all nodes at level l must be chosen before any nodes in level l + 1. The number of different orderings at any level is the number of permutations for the nodes at that level. This results in

a lower bound for a dag. The upper bound may be calculated by using a completely unconnected graph. The function is then simply

This is simply the number of permutations of all the nodes. This is the upper bound for a dag and represents the ultimate in flexibility. As the number of orderings increase, the number of different final schedules increase, allowing a scheduler more opportunities to create good schedules. A difficulty with reducing the number of edges is the resultant increase in the size of the search space. To make use of the increased flexibility, a powerful search technique must be used.

Recent work by Brightwell and Winkler [BW90] has shown that determining the actual number of total orders in a dag, given a partial ordering, is #P-complete. That is, the problem is at least as hard as finding all the Hamiltonian circuits existing in a graph [GJ79]. #P-complete enumeration problems are thought to be "harder" than their corresponding NP-complete existence problems. For example, if P=NP, and it could be shown in polynomial time that an arbitrary graph contains a Hamiltonian circuit, it is not apparent that this would provide a polynomial time method of knowing how many Hamiltonian circuits exist. This has a large impact on the existing methods of instruction scheduling.

#### 2.3 Dags to Represent Data Dependence

Data dependence between operations in a program is usually represented in a data dependence dag (DDD). Data dependence concepts and standard terminology are widely discussed in the literature [BSKT79, PKL80, Veg82, PW86, Ban88]. The three basic types of data dependence are

• Flow Dependence — sometimes called true dependence or data dependence. An operation  $m_2$  is flow dependent on operation  $m_1$  if  $m_1$  executes before  $m_2$ and  $m_1$  writes to some memory location read by  $m_2$ . (This is read-after-write dependency.)

- Anti-Dependence sometimes called false dependence. An operation m<sub>2</sub> is anti-dependent on operation m<sub>1</sub> if m<sub>1</sub> executes before m<sub>2</sub> and m<sub>2</sub> writes to some memory location read by m<sub>1</sub>, thereby destroying the value read by m<sub>1</sub>. (This is write-after-read dependency.)

- Output Dependence An operation  $m_2$  is output dependent on operation  $m_1$  if  $m_1$  executes before  $m_2$  and  $m_2$  and  $m_1$  both write to the same location. (This is write-after-write dependency.)

For completeness (with two operations: read and write, taken two ways), it may be noted that read-after-read usually does not create a dependency and therefore does not require an edge in the graph. Reading a value multiple times does not destroy it, except in the presence of volatile resources. If, for example, reading from a port removes a value from a queue and the next value from the queue is placed in the port, an edge is required so the reading occurs in the order specified in the source. This type of edge can be termed an *input dependence* edge.

A code fragment is illustrative

```

first_char = readchar (port1); /* 1 */

second_char = readchar (port1); /* 2 */

if (first_char == 'a')

...

```

Here, there is no data dependence between statements (1) and (2) intimating their order of operation is unimportant. However the order of operation must be preserved in the resultant code in order to retain program semantics. An input dependency edge must be added to reflect this. Output dependencies can result from writing similar volatile machine resources.

## 2.3.1 Necessary Edges

Of the four types of edges, only true dependency edges are usually required for program correctness. These result from the expression of semantics in the source. In the presence of volatile resources, input and output dependencies can be added to express the lexical ordering of operations <sup>3</sup>.

Without volatile resources, read-after-read does not destroy information and therefore requires no edge in the DDD. Also, without volatile resources the other two are remnants from decisions made by the translation from the source. This is a reflection of modern architectures and languages. In architectures, a write to a resource destroys information that might be needed later. In non-single-assignment languages, variables may hold different values during the course of program execution. A variable's value is well defined by language rules such as lexical ordering and control flow constructs.

A write-after-write dependency reflects dead code, either in the source program or in operations generated by the compiler. A dead code removal phase should remove these dependencies before instruction scheduling occurs. Write-after-read dependencies are created by the desire to reuse a resource before its value has been used for the last time. The removal of this type of dependency has a large impact upon the resulting schedule. Resource binding should occur as late as possible to ameliorate this impact. Section 3.4 and Sweany and Beaty [SB90] discuss a method of delaying resource binding so fewer anti-dependencies will exist in a DDD. When there are not enough resources of the necessary type to hold all values live at a point in the program, anti-dependencies may have to be introduced.

Edges in a DDD describe the order the operations must appear in the *final* schedule. It does not restrict the order operations may be placed during scheduling. The reason for this emphasis will be apparent.

<sup>&</sup>lt;sup>3</sup>Volatile resources are easy to model in ROCKET.

#### 2.4 Timing on Edges

In the previous definition of the Local Compaction Problem, a function  $\delta(e)$ specified the duration of an operation. This is the amount of time after an operation start its value is ready for use. If  $\delta(e) = 0$ , then a  $\leq$  relation is defined by the edge. If  $\delta(e) > 0$  then a  $\prec$  relation is defined by the edge. The  $\delta(e)$  allows for expression of multi-cycle operations. It does not allow expression of operations having either transient results or results latched into a resource upon completion. These types are prevalent in architectures that, for example, contain visible pipe stages.

In order to model these two types of resources, a new function  $\Delta(e)$  is defined.  $\Delta(e)_{min,max}$  specifies the range the output from an operation is valid. That is, if op is scheduled at time T, the resultant value may be used any time from T + min to T + max. For operations that latch their output,  $t = \infty$ . Edges in the DDD are then labeled with their corresponding  $\Delta(e)$  values. This allows for great flexibility in describing architectural features to the scheduler.

With the addition of  $\Delta(e)$ , more machine features can be described, allowing the scheduler to remove some of the hardware requirements in the processor. If the scheduler can operate directly on a DDD with  $\Delta(e)$  specifying an operation's duration range, a larger variety of architectural features can be exploited. For example, synchronous pipes may be directly modeled and scheduled as easily as other operations. The need for explicit pipe advances is not needed (although they can be modeled as well, if needed.)

Pipes doing arithmetic on integer and floating point types usually have varying completion times. For example, an add can take two cycles, a multiply 11, and a division 19. Some pipes have transient outputs, requiring  $\Delta(e)_{min,max}\{min,max \mid min \leq max < \infty\}$ . If the pipe operation includes a destination resource, the use of the value may occur any time after the operation's completion:  $\Delta(e)_{min,max}\{min,max \mid min \leq max = \infty\}$ . Individual pipe stages can be modeled with chains of operations. For example, a multi-stage pipe operation of length L can be modeled with  $\Delta(e)_{min,max}\{min,max \mid min = max = L\}$ . Another approach, possibly exposing more of the actual hardware implementation, is to model each stage of the pipe individually, each separated by  $\Delta(e\star)_{min,max} = \{min,max \mid min = max = 1\}$ . In this case,  $e\star$  represents a stage of the entire pipelined operation. The entire pipe is then modeled by the chain

$$\sum_{1}^{L} \Delta(e\star)$$

where L is the length of the pipe.

When this approach of modeling each stage in a pipe is used, it simulates a pipe reservation station at code generation time. This reduces the amount of hardware resources needed in the pipe by guaranteeing that operation semantics are preserved. Hennessy et al. [HJP<sup>+</sup>82] <sup>4</sup> give several reasons for shifting complexity from the hardware to the software:

- the complexity is paid for only once (during compilation) and therefore the architectural overhead required otherwise is not present during the execution of all programs, and

- 2. allows the concentration of effort on software instead of a complex hardware engine.

Software is not necessarily easier to design but can pay more dividends on time spent. If a function can be handled in software, more chip space will be left for functionality that cannot either be derived in software or will benefit greatly from its on-chip inclusion.

<sup>&</sup>lt;sup>4</sup>There they use "MIPS" to denote Microprocessor without Interlocked Pipeline Stages.

#### 2.5 Timing on Nodes

If only  $\delta(e)$  is used, only the for an operation minimum time  $\theta(op)$  can be calculated. The calculation is simply the longest path from the roots of the DDD to *op*. This produces the earliest instruction  $\iota$  that *op* can be scheduled.  $\iota$  is used during scheduling as the basis for placement within the instruction list.  $\theta(op)$  is sufficient for machines where  $\delta(e)$  is sufficient to describe the architecture. The assumption is the maximum timing for  $\delta(e) = \infty$ .

## 2.5.1 Absolute Timing

When an architecture description requires the use of non-infinite maximum timing by  $\Delta(e)$ , the simple node timing algorithm must also be updated. With the definition of  $\Delta(e)$  on edges, timing can be assigned to the nodes (operations) as well. Using  $\Delta(e)$ , a range of values the operation can be scheduled in can be calculated. This range will be termed  $\Theta(op)_{min,max}$  meaning op can be scheduled in instruction  $\iota\{\iota \mid min \leq \iota \leq max\}$ . This is termed the *absolute timing* for op. Figure 2.2 displays the algorithm for calculating the absolute timing for the nodes in a DDD given in [AM88].

The addition and subtraction operations above must take into account the possibility of  $\infty$  values.

The idea behind the algorithm is to keep the operations as early as possible but as late as necessary. Keeping them as early as possible allows for better scheduled results by creating more flexible DDDs. Because operations must remain in semantic order, increasing their start times may be necessary. Note that either successors or predecessors of a node can change the range where its operation is valid.

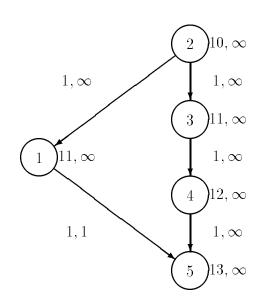

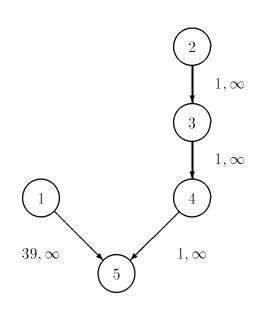

A complication not addressed in [AM88] is the possibility of legal loops in the timing. In Figure 2.3, if the absolute timing algorithm is run, the following occurs:

1. Starting with  $\Theta(2) = (10, \infty)$ :  $\Theta(1) = (11, \infty), \Theta(3) = (11, \infty).$

```

set_time (node)

{

for each successor, succ, of node

ł

if update_time (succ, node, SUCC) alters timing for succ

ł

set_time (succ);

}

for each predecessor, pred, of node

if update_time (pred, node, PRED) alters timing for pred

ł

set_time (pred);

}

}

}

update_time (this_op, prev_op, direction)

if (direction == PRED)

{

\Theta(this\_op)_{min} = \max(\Theta(this\_op)_{min},

\Theta(prev\_op)_{min} - \Delta(prev\_op \rightarrow this\_op)_{max});

\Theta(this\_op)_{max} = \min(\Theta(this\_op)_{max},

\Theta(prev\_op)_{max} - \Delta(prev\_op \rightarrow this\_op)_{min});

}

else // direction == SUCC

ł

\Theta(this\_op)_{min} = \max(\Theta(this\_op)_{min},

\Theta(prev\_op)_{min} + \Delta(prev\_op \rightarrow this\_op)_{min});

\Theta(this\_op)_{max} = \min(\Theta(this\_op)_{max},

\Theta(prev\_op)_{max} + \Delta(prev\_op \rightarrow this\_op)_{max});

}

}

```

Figure 2.2: Original absolute timing algorithm

Figure 2.3: A graph where the absolute timing algorithm can fail

- 2. Recurse to  $\Theta(3)$ :  $\Theta(4) = (12, \infty)$ .

- 3. To  $\Theta(4)$ .  $\Theta(5) = (13, \infty)$ .

- 4. At  $\Theta(5)$ , change predecessors:  $\Theta(1) = (12, \infty), \Theta(4)$  unchanged.

- 5. Recurse to  $\Theta(1)$ , change predecessors:  $\Theta(2) = (11, \infty)$ , goto 1.

The difficulty occurs because the routine follows a  $(n, \infty)$  edge to a previous node, changing its timing. An important observation is

there is no reason to follow  $(n, \infty)$  edges to predecessors. The absolute timing algorithm is only interested in making the timing on nodes *later*, and with  $\infty$  maximum timing on an edge, no reason exists to make a predecessor node later. The operation may occur as early as possible and the value will remain valid forever.

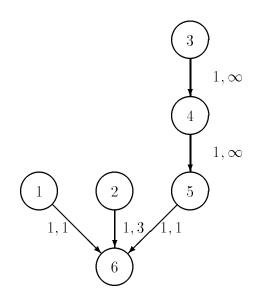

With this observation, a revised algorithm may be created. The routine in Figure 2.4 defines how successor node's timings are updated.

The assertions check for timing errors. For example, a timing error is created when, for a scheduled node, its time must be updated in order to fulfill the constraints of the surrounding nodes. This is an obvious impossibility as a scheduled node has its timing completely restricted. Also, for example, if a node's earliest time becomes later than its latest time, a timing error with respect to its neighbors is present. The assertions provide a means for detecting timing errors in the DDD when the order of packing being attempted is erroneous. This has the same result as *extended timings* [SDX87] have, although not necessarily as early in the scheduling process.

To correctly set predecessor times, the routine in Figure 2.5 may be used. The assertions for this routine are similar, they also check to see whether the timing is still valid.

```

update_succ_time (prev_op, this_op)

changed = FALSE;

if (\Theta(this\_op)_{min} < \Theta(prev\_op)_{min} + \Delta(prev\_op \rightarrow this\_op)_{min})

{

assert (!scheduled);

\Theta(this\_op)_{min} = \Theta(prev\_op)_{min} + \Delta(prev\_op \to this\_op)_{min}

changed = TRUE;

if (\Theta(this\_op)_{max} > \Theta(prev\_op)_{max} + \Delta(prev\_op \rightarrow this\_op)_{max})

{

assert (!scheduled);

\Theta(this\_op)_{max} = \Theta(prev\_op)_{max} + \Delta(prev\_op \rightarrow this\_op)_{max}

changed = TRUE;

}

assert (\Theta(this\_op)_{min} \ge \Theta(prev\_op)_{min} + \Delta(prev\_op \rightarrow this\_op)_{min});

assert (\Theta(this\_op)_{min} \leq \Theta(prev\_op)_{max} + \Delta(prev\_op \rightarrow this\_op)_{max});

assert (\Theta(this\_op)_{max} \ge \Theta(prev\_op)_{min} + \Delta(prev\_op \rightarrow this\_op)_{min});

assert (\Theta(this\_op)_{max} \leq \Theta(prev\_op)_{max} + \Delta(prev\_op \rightarrow this\_op)_{max});

assert (\Theta(this\_op)_{min} < \infty);

assert (\Theta(this\_op)_{min} > 0);

assert (\Theta(this\_op)_{min} \leq \Theta(this\_op)_{max});

return changed;

```

ł

}

Figure 2.4: Update successor timing

```

update_pred_time (succ_op, this_op)

{

if (\Delta(prev\_op \rightarrow this\_op)_{max} = \infty)

ł

return FALSE;

changed = FALSE;

if (\Theta(this\_op)_{min} < \Theta(succ\_op)_{min} - \Delta(succ\_op \rightarrow this\_op)_{max});

ł

assert (!scheduled);

\Theta(this\_op)_{min} = \Theta(succ\_op)_{min} - \Delta(succ\_op \to this\_op)_{max});

changed = TRUE;

if (\Theta(this\_op)_{max} > \Theta(prev\_op)_{max} - \Delta(prev\_op \rightarrow this\_op)_{min});

ł

assert (!scheduled);

\Theta(this\_op)_{max} = \Theta(prev\_op)_{max} - \Delta(prev\_op \to this\_op)_{min});

changed = TRUE;

}

assert (\Theta(this\_op)_{min} \ge \Theta(prev\_op)_{min} - \Delta(prev\_op \rightarrow this\_op)_{max});

assert (\Theta(this\_op)_{min} \leq \Theta(prev\_op)_{max} - \Delta(prev\_op \rightarrow this\_op)_{min});

assert (\Theta(this\_op)_{max} \ge \Theta(prev\_op)_{min} - \Delta(prev\_op \rightarrow this\_op)_{max});

assert (\Theta(this\_op)_{max} \leq \Theta(prev\_op)_{max} - \Delta(prev\_op \rightarrow this\_op)_{min});

assert (\Theta(this\_op)_{min} < \infty);

assert (\Theta(this\_op)_{min} > 0);

assert (\Theta(this\_op)_{min} \leq \Theta(this\_op)_{max});

return changed;

```

Figure 2.5: Update predecessor timing

}

Nota bene: there are two possibilities worth consideration when computing  $\Theta(op)_{min}$  for a predecessor node:

1.

$$\Theta(this\_op)_{min} = \Theta(succ\_op)_{min} - \Delta(succ\_op \rightarrow this\_op)_{max}$$

2.

$$\Theta(this\_op)_{min} = \Theta(succ\_op)_{min} - \Delta(succ\_op \rightarrow this\_op)_{min}$$

Both produce valid  $\Theta(op)_{min}$ . The first produces more liberal  $\Theta(op)_{min}$  allowing more flexibility during scheduling and is therefore chosen. The same logic may be used in calculating  $\Theta(op)_{max}$  for a predecessor node.

These two routines guarantee  $\Theta(op)$  is within the permissible range. If it already is, they do not change it. Notice it is an error to change the timing to be earlier than it currently is. The node is as early as it can be in relation to some node; if another requires it earlier a timing error is present.

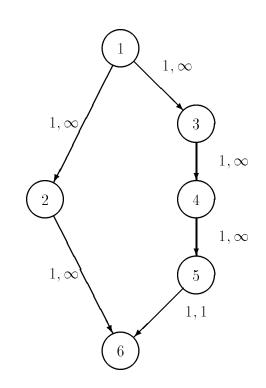

As before, a recursive routine may be used to calculate the correct absolute timing for an entire DDD (Figure 2.6.) The recursive method has the impediment of possibly visiting a node multiple times to correctly set its absolute timing. A better method would only visit a successor (predecessor) node once all its predecessors (successors) had been visited. This is possible by setting the absolute timing in successor nodes in a reverse postfix depth-first order, and similarly the predecessor nodes in a postfix depth-first order. Whenever an entire traversal in either direction is made without any absolute timing changing, the method may stop. In this way, nodes are visited as few times as possible.

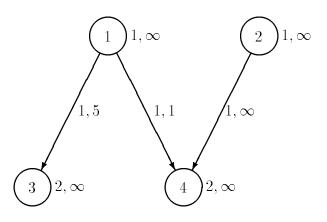

The subgraph in Figure 2.7 demonstrates the need to iterate an undetermined number of times. Consider the following flow of events:

- 1. Originally, nodes 1 and 2 are set to  $1, \infty$  and node 3 and 4 are set to  $2, \infty$ .

- 2. Because of timing (not visible in the subgraph), node 2's timing changes to  $15, \infty$ .

```

update_time (node)

{

for each succ_node in node.successors

{

if (update_succ_time (node, succ_node))

ł

update_time (succ_node);

}

for each pred_node in node.predecessors

ł

if (update_succ_time (node, pred_node))

{

update_time (pred_node);

}

}

}

```

Figure 2.6: Update timing

Figure 2.7: Example for the need to iterate

- 3. A pass down through the graph notices that node 2's timing has changed, necessitating the possible updating of its successors and predecessors.

- 4. Node 4's time is updated to  $16, \infty$ . Node 1 and 3 are unaffected.

- 5. On a pass back up, node 4's timing changed in the previous path, and its neighbors must be updated. Node 1's timing is changed to  $15, \infty$  due to the restricted edge from node 4.

- 6. This leaves node 3 in need of updating, and another pass must be made to reflect this.

# 2.6 Summary

This chapter has shown how difficult the general scheduling problem, and a specific instance: the Local Compaction Problem, are. Scheduling problems are usually represented in a directed acyclic graph, giving a partial order to the operations. Enumerating all total orders consistent with a partial order in a dag is shown to be #P-complete. Dags are used to represent the data dependence information in the Local Compaction Problem using extensions to model both architecture-specific and translation-related information.

# Chapter 3

## COMPILER TECHNOLOGY

There are many different phases involved in producing quality code from a high level language algorithm description. Many are familiar to compiler writers and can be found in Aho et al. [ASU86]. These include lexical analysis, parsing, dead code removal, loop invariant code hoisting, induction variable simplification, operator strength reduction, constant folding, copy propagation and common subexpression elimination. These code improvement routines are more difficult to implement for MILCs because it is not known whether an apparent improvement actually decreases the time or space in the resulting program.

# 3.1 MILC Complexities

As an example of how MILCs can complicate traditional optimizations, consider hoisting a loop invariant expression out of a loop and into its header. If the expression does not add to the length of the scheduled code within the loop boundary but adds instructions when placed above, because of resource or encoding conflicts, then the "optimization" is not an optimization at all. Leaving the expression in the loop, and recomputing it each time the loop executes, costs nothing in time and space. With this in mind it can be seen that simple minded code improvements need good heuristics or proper feedback to do their job well.

Phases not usually found in compilers generating code for traditional machines are also present. In MILCs, more options exist in choosing resource bindings. An integer for example may reside in an integer register, a floating point register, an address register, an external memory, a graphics vector or a volatile latch within the machine. The choice for where to place an arbitrary integer then becomes one of great difficulty, also having a large impact on the resulting code. The information needed to make a good choice is usually available too late in the compilation process to do any good. Only after instruction scheduling has completed is information known about unused machine resources, and instruction scheduling cannot complete without all values being bound to a machine resource. In simpler machines, there are fewer choices about the placement of values into resources.

The scheduling of computations to functional units is another difficult process in MILCs. With replicated functional units or units with redundant capabilities (such as floating point units that can also do integer arithmetic), choosing where a computation is performed is difficult. Work done in scheduling problems in operating systems might be applicable here but finding an optimal solution is certainly computationally intractable. With simpler machines, there exist very few functional units to do calculations and so the choice is trivial. The difficulty in the ordering of translation processes has been termed the *phase coupling* problem, and Allan [AM87] discusses different approaches attempting to reduce its impact.

Many of the code improvement routines require a large amount of analysis to perform effectively. These must preserve the semantics of the original code while producing as flexible a representation as possible to operate upon. These analyses include:

• Dataflow analysis. Local dataflow analysis computes the uses and definitions for all variables within a basic block. Global dataflow analysis uses this information to form live-in and live-out sets for each basic block. This allows complete dataflow information to be found for a function, allowing the use of semantic-preserving transformations and correct register save and restore operations. If the dataflow procedures look beyond the function boundaries to encompass the entire program, the information is more accurate and less conservative transformations may take place. The intelligent passing of parameters is a particularly rich area for these transformations.

- Dominator analysis. Dominator relationship provides a partial ordering of basic blocks within a function. A block A is said to dominate a block B if all paths to B pass through A. This reveals the loop structures within a function, for example.

- Symbolic evaluation, origin, and cover analysis. These analyses provide, for each expression, a completely expanded expression based upon previous expressions and initial values, and are discussed by Reif and Tarjan in [RT81]. They provide information as to the origin of each expression, useful in delimiting the amount of code motion allowable while maintaining program semantics. They are also used to remove global common subexpressions and to propagate both copies and constants globally.